Payment Method

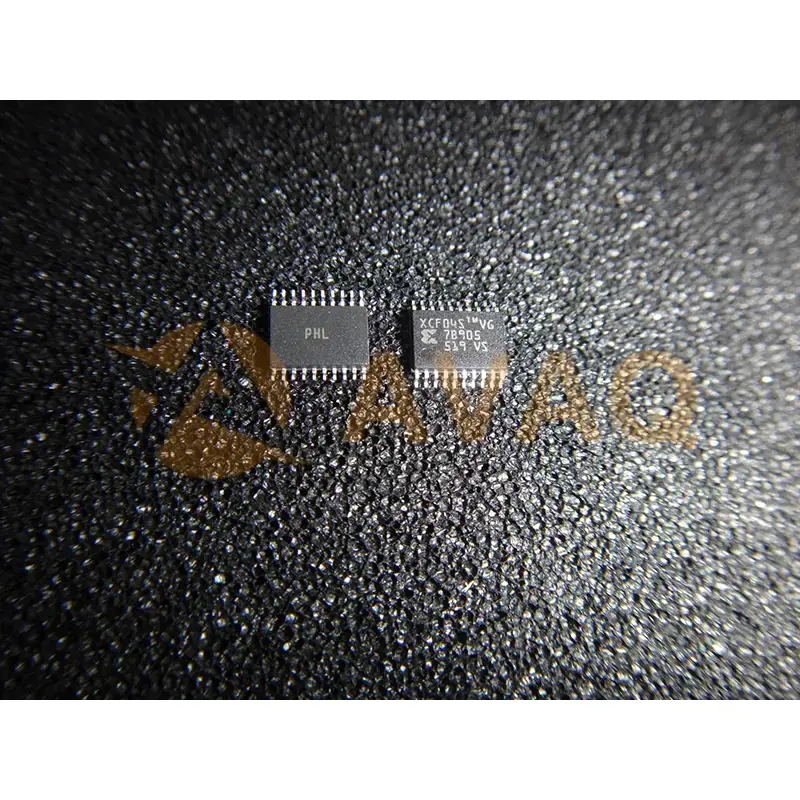

FPGA Configuration PROM Parallel/Serial 1M-bit 2.5V/3.3V 20-Pin SOIC

SOP20Manufacturer:

Mfr.Part #:

XC18V01SOG20C

Datasheet:

Place:

Republic of Korea

Launch_date:

Feb 3, 1999

Last_inspection_date:

01 AUG 2022

Supplier_cage_code:

68994

EDA/CAD Models:

Please fill in the short form below and we will provide you the quotation immediately.

Xilinx introduces the XC18V00 series of in-system programmable configuration PROMs (Figure 1). Devices in this 3.3V family include a 4-megabit, a 2-megabit, a 1-megabit, and a 512-kilobit PROM that provide an easy-touse, cost-effective method for reprogramming and storing Xilinx FPGA configuration bitstreams.

When the FPGA is in Master Serial mode, it generates a configuration clock that drives the PROM. A short access time after CE and OE are enabled, data is available on the PROM DATA (D0) pin that is connected to the FPGA DIN pin. New data is available a short access time after each rising clock edge. The FPGA generates the appropriate number of clock pulses to complete the configuration. When the FPGA is in Slave Serial mode, the PROM and the FPGA are clocked by an external clock.

When the FPGA is in Master SelectMAP mode, the FPGA generates a configuration clock that drives the PROM. When the FPGA is in Slave Parallel or Slave SelectMAP mode, an external oscillator generates the configuration clock that drives the PROM and the FPGA. After CE and OE are enabled, data is available on the PROM’s DATA (D0-D7) pins. New data is available a short access time after each rising clock edge. The data is clocked into the FPGA on the following rising edge of the CCLK. A free-running oscillator can be used in the Slave Parallel or Slave SelecMAP modes.

Multiple devices can be cascaded by using the CEO output to drive the CE input of the following device. The clock inputs and the DATA outputs of all PROMs in this chain are interconnected. All devices are compatible and can be cascaded with other members of the family or with the XC17V00 one-time programmable serial PROM family.

| place | Republic of Korea | launch_date | Feb 3, 1999 |

| last_inspection_date | 01 AUG 2022 | supplier_cage_code | 68994 |

| htsusa | 8542320051 | schedule_b | 8542320050 |

| ppap | False | aec | False |

After-Sales & Settlement Related

Payment

Payment

Payment Method

For alternative payment channels, please reach out to us at:

[email protected] Shipping & Packing

Shipping & Packing

Shipping Method

AVAQ determines and packages all devices based on electrostatic discharge (ESD) and moisture sensitivity level (MSL) protection requirements.

Warranty

Warranty

365-Day Product

Quality Guarantee

We promise to provide 365 days quality assurance service for all our products.

| Qty. | Unit Price | Ext. Price |

|---|---|---|

| 1+ | - | - |

The prices below are for reference only.

All bill of materials (BOM) can be sent via email to ![]() [email protected],

or fill below form to Quote for XC18V01SOG20C, guaranteed quotes back within

[email protected],

or fill below form to Quote for XC18V01SOG20C, guaranteed quotes back within

![]() 12hr.

12hr.

XCF04SVOG20C

AMD Xilinx, Inc

30+ $149.680

XCF01SVOG20C

AMD Xilinx, Inc

FPGA Configuration PROM Memory

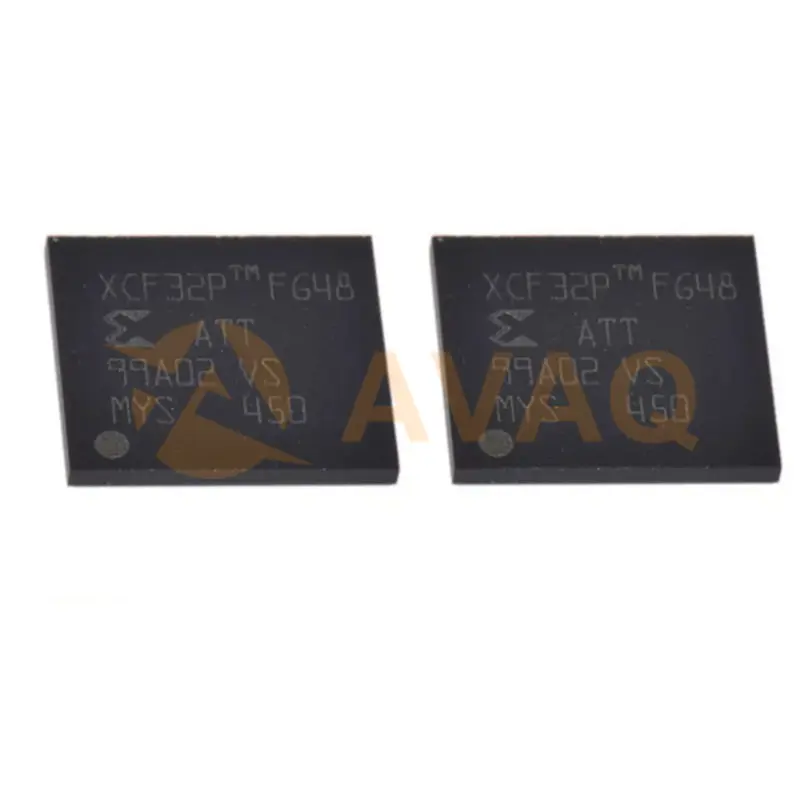

XCF32PFSG48C

AMD Xilinx, Inc

FPGA Configuration PROM Memory

XCF32PFS48C

AMD Xilinx, Inc

FPGA Configuration PROM Memory

XCF08PVOG48C

AMD Xilinx, Inc

XCF08PVOG48C, Configuration Memory 1.65 → 2 V 48-Pin TSOP

Solder instead of dead in the thermometer-works.