Payment Method

Telecom IC, CMOS, PBGA208,

Manufacturer:

Microchip Technology

Mfr.Part #:

PM4354-NGI

Datasheet:

ECCN (US):

5A991.b

Automotive:

No

PPAP:

No

Number of Transceivers:

4

EDA/CAD Models:

Please fill in the short form below and we will provide you the quotation immediately.

| ECCN (US) | 5A991.b | Part Status | Obsolete |

| Automotive | No | PPAP | No |

| Number of Transceivers | 4 | Standard Framing Format | E1|J1|T1 |

| Mounting | Surface Mount | PCB changed | 208 |

| Pin Count | 208 | Lead Shape | Ball |

After-Sales & Settlement Related

Payment

Payment

Payment Method

For alternative payment channels, please reach out to us at:

[email protected] Shipping & Packing

Shipping & Packing

Shipping Method

AVAQ determines and packages all devices based on electrostatic discharge (ESD) and moisture sensitivity level (MSL) protection requirements.

Warranty

Warranty

365-Day Product

Quality Guarantee

We promise to provide 365 days quality assurance service for all our products.

| Qty. | Unit Price | Ext. Price |

|---|---|---|

| 1+ | - | - |

The prices below are for reference only.

All bill of materials (BOM) can be sent via email to ![]() [email protected],

or fill below form to Quote for PM4354-NGI, guaranteed quotes back within

[email protected],

or fill below form to Quote for PM4354-NGI, guaranteed quotes back within

![]() 12hr.

12hr.

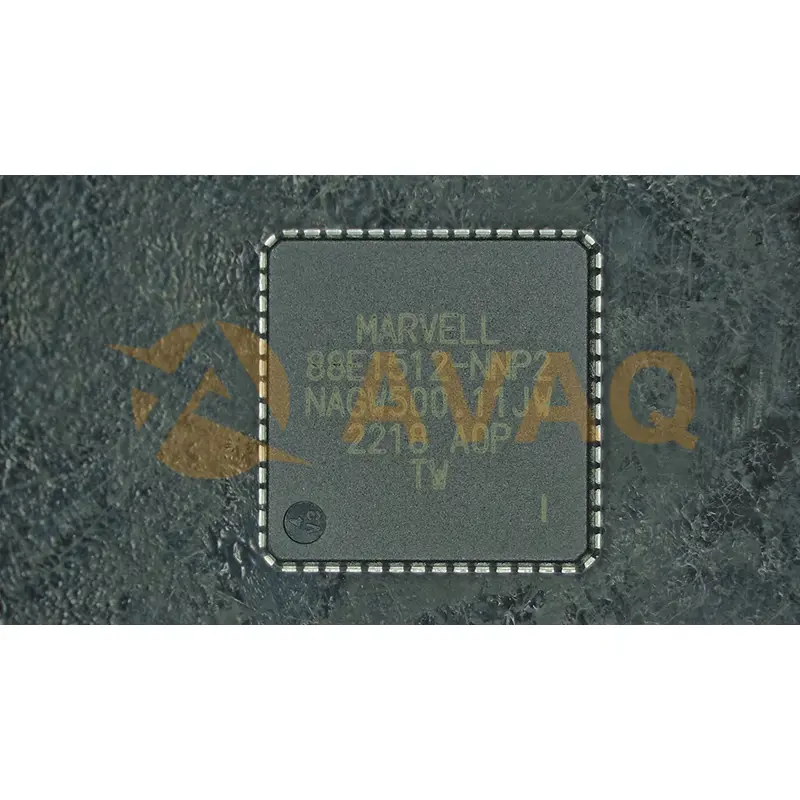

88E1512-A0-NNP2I000

Marvell

1040+ $3.688

SFH485P

ams OSRAM

Infrared Emitter 880nm 5mW/sr Circular Top Mount 2-Pin T-1 3/4 T/R

XP1001000-05R

Lantronix, Inc.

French Electronic Distributor since 1988

KSZ9897RTXI

MICROCHIP TECHNOLOGY INC

7-Port Gigabit Ethernet Switch with SGMII/RGMII/MII/RMII.

DP83867ERGZT

TEXAS INSTRUMENTS INC

Extended temperature, robust low-latency gigabit Ethernet PHY transceiver with SGMII