Payment Method

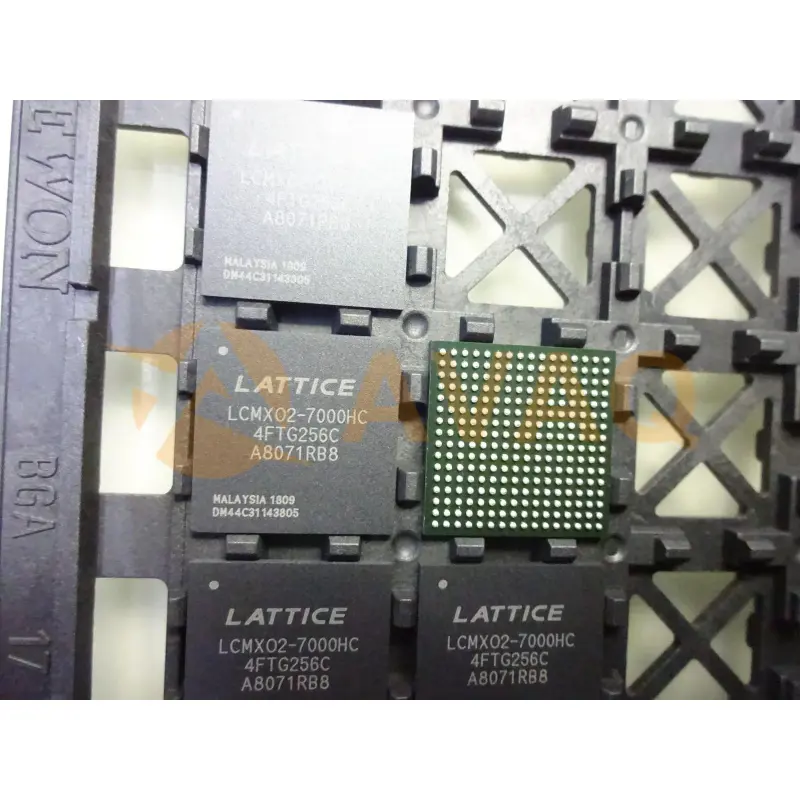

MachXO2 Field Programmable Gate Array (FPGA) IC 206 245760 6864 256-LBGA

Manufacturer:

Lattice Semiconductor Corporation

Mfr.Part #:

LCMXO2-7000HC-4FTG256C

Datasheet:

Pbfree Code:

Yes

Part Life Cycle Code:

Active

Reach Compliance Code:

compliant

ECCN Code:

3A991.D

EDA/CAD Models:

Please fill in the short form below and we will provide you the quotation immediately.

MachXO2 Field Programmable Gate Array (FPGA) IC 206 245760 6864 256-LBGA

| Pbfree Code | Yes | Part Life Cycle Code | Active |

| Reach Compliance Code | compliant | ECCN Code | 3A991.D |

| HTS Code | 8542.39.00.01 | Additional Feature | ALSO OPERATES AT 3.3 V NOMINAL SUPPLY |

| JESD-30 Code | S-PBGA-B256 | JESD-609 Code | e1 |

| Length | 17 mm | Moisture Sensitivity Level | 3 |

| Number of Inputs | 206 | Number of Logic Cells | 6864 |

| Number of Outputs | 206 | Number of Terminals | 256 |

| Operating Temperature-Max | 85 °C | Operating Temperature-Min | |

| Packing Method | TRAY | Peak Reflow Temperature (Cel) | 260 |

| Programmable Logic Type | FIELD PROGRAMMABLE GATE ARRAY | Qualification Status | Not Qualified |

| Seated Height-Max | 1.55 mm | Supply Voltage-Max | 3.465 V |

| Supply Voltage-Min | 2.375 V | Supply Voltage-Nom | 2.5 V |

| Surface Mount | YES | Temperature Grade | OTHER |

| Terminal Finish | Tin/Silver/Copper (Sn/Ag/Cu) | Terminal Form | BALL |

| Terminal Pitch | 1 mm | Terminal Position | BOTTOM |

| Time@Peak Reflow Temperature-Max (s) | 30 | Width | 17 mm |

After-Sales & Settlement Related

Payment

Payment

Payment Method

For alternative payment channels, please reach out to us at:

[email protected] Shipping & Packing

Shipping & Packing

Shipping Method

AVAQ determines and packages all devices based on electrostatic discharge (ESD) and moisture sensitivity level (MSL) protection requirements.

Warranty

Warranty

365-Day Product

Quality Guarantee

We promise to provide 365 days quality assurance service for all our products.

| Qty. | Unit Price | Ext. Price |

|---|---|---|

| 1+ | $23.058 | $23.06 |

| 200+ | $8.924 | $1,784.80 |

| 500+ | $8.610 | $4,305.00 |

| 1000+ | $8.455 | $8,455.00 |

The prices below are for reference only.

All bill of materials (BOM) can be sent via email to ![]() [email protected],

or fill below form to Quote for LCMXO2-7000HC-4FTG256C, guaranteed quotes back within

[email protected],

or fill below form to Quote for LCMXO2-7000HC-4FTG256C, guaranteed quotes back within

![]() 12hr.

12hr.