Payment Method

CPLD - Complex Programmable Logic Devices PROGRAMMABLE SUPER FAST HI DENSITY PLD

QFP48Manufacturer:

Mfr.Part #:

LC4032V-75TN48I

Datasheet:

Pin Count:

48

Released Date:

May 10, 2019

Last Modified Date:

Mar 7, 2023 4:10 PM UTC

EDA/CAD Models:

Please fill in the short form below and we will provide you the quotation immediately.

The high performance ispMACH 4000 family from Lattice offers a SuperFAST CPLD solution. The family is a blend of Lattice’s two most popular architectures: the ispLSI® 2000 and ispMACH 4A. Retaining the best of both families, the ispMACH 4000 architecture focuses on significant innovations to combine the highest performance with low power in a flexible CPLD family.

The ispMACH 4000 combines high speed and low power with the flexibility needed for ease of design. With its robust Global Routing Pool and Output Routing Pool, this family delivers excellent First-Time-Fit, timing predictability, routing, pin-out retention and density migration.

The ispMACH 4000 family offers densities ranging from 32 to 512 macrocells. There are multiple density-I/O combinations in Thin Quad Flat Pack (TQFP), Chip Scale BGA (csBGA) and Fine Pitch Thin BGA (ftBGA) packages ranging from 44 to 256 pins/balls. Table 1 shows the macrocell, package and I/O options, along with other key parameters.

The ispMACH 4000 family has enhanced system integration capabilities. It supports 3.3V (4000V), 2.5V (4000B) and 1.8V (4000C/Z) supply voltages and 3.3V, 2.5V and 1.8V interface voltages. Additionally, inputs can be safely driven up to 5.5V when an I/O bank is configured for 3.3V operation, making this family 5V tolerant. The ispMACH 4000 also offers enhanced I/O features such as slew rate control, PCI compatibility, bus-keeper latches, pull-up resistors, pull-down resistors, open drain outputs and hot socketing. The ispMACH 4000 family members are 3.3V/ 2.5V/1.8V in-system programmable through the IEEE Standard 1532 interface. IEEE Standard 1149.1 boundary scan testing capability also allows product testing on automated test equipment. The 1532 interface signals TCK, TMS, TDI and TDO are referenced to VCC (logic core).

| Pin Count | 48 | Released Date | May 10, 2019 |

| Last Modified Date | Mar 7, 2023 4:10 PM UTC |

After-Sales & Settlement Related

Payment

Payment

Payment Method

For alternative payment channels, please reach out to us at:

[email protected] Shipping & Packing

Shipping & Packing

Shipping Method

AVAQ determines and packages all devices based on electrostatic discharge (ESD) and moisture sensitivity level (MSL) protection requirements.

Warranty

Warranty

365-Day Product

Quality Guarantee

We promise to provide 365 days quality assurance service for all our products.

| Qty. | Unit Price | Ext. Price |

|---|---|---|

| 1+ | - | - |

The prices below are for reference only.

All bill of materials (BOM) can be sent via email to ![]() [email protected],

or fill below form to Quote for LC4032V-75TN48I, guaranteed quotes back within

[email protected],

or fill below form to Quote for LC4032V-75TN48I, guaranteed quotes back within

![]() 12hr.

12hr.

LCMXO2-1200HC-4TG100I

LATTICE

1000+ $3.419

LCMXO2-1200HC-4TG100C

LATTICE

1000+ $2.604

LC4032V-75TN48C

Lattice

High Performance E2 CMOS PLD Generic Array Logic

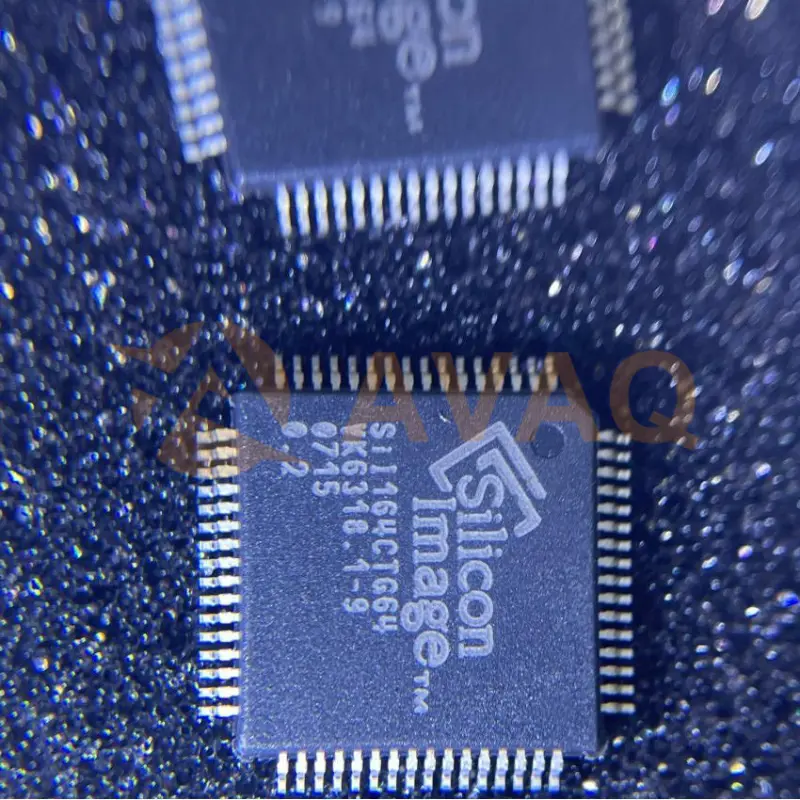

SiI164CTG64

Lattice

TQFP package Transmitter with 2 transmitters

LCMXO2-640HC-4TG100C

Lattice

ROHS Programmable Logic Device (CPLDs/FPGAs) 640 80 TQFP-100(14x14) LCMXO2-640HC-4TG100C

Packed in a normal package. How did it not break when delivered?! Must be a miracle.