Payment Method

Analog & Digital Crosspoint ICs 3.3V 160 I/O

Manufacturer:

Mfr.Part #:

ispGDX160VA-5B208

Datasheet:

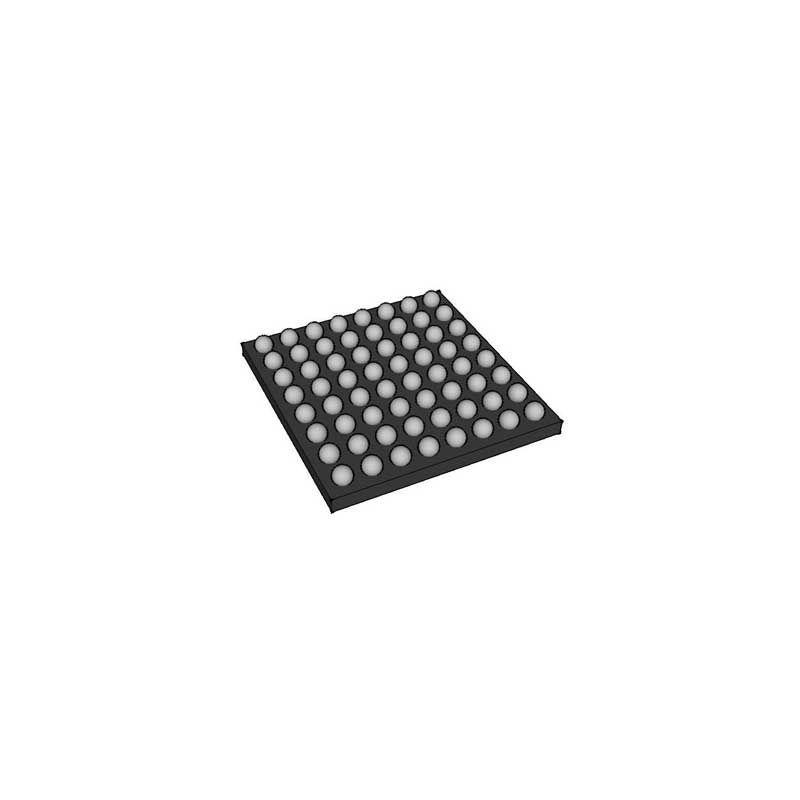

Package/Case:

BGA

Product Type:

Lifecycle:

Obsolete

EDA/CAD Models:

Please fill in the short form below and we will provide you the quotation immediately.

The ispGDXV/VA architecture provides a family of fast, flexible programmable devices to address a variety of system-level digital signal routing and interface requirements including:

• Wide Data and Address Bus Multiplexing (e.g. 16:1 High-Speed Bus MUX)

• Programmable Control Signal Routing (e.g. Interrupts, DMAREQs, etc.)

• Board-Level PCB Signal Routing for Prototyping or Programmable Bus Interfaces

The devices feature fast operation, with input-to-output signal delays (Tpd) of 3.5ns and clock-to-output delays of 3.5ns.

The architecture of the devices consists of a series of programmable I/O cells interconnected by a Global Routing Pool (GRP). All I/O pin inputs enter the GRP directly or are registered or latched so they can be routed to the required I/O outputs. I/O pin inputs are defined as four sets (A,B,C,D) which have access to the four MUX inputs found in each I/O cell. Each output has individual, programmable I/O tri-state control (OE), output latch clock (CLK), clock enable (CLKEN), and two multiplexer control (MUX0 and MUX1) inputs. Polarity for these signals is programmable for each I/O cell. The MUX0 and MUX1 inputs control a fast 4:1 MUX, allowing dynamic selection of up to four signal sources for a given output. A wider 16:1 MUX can be implemented with the MUX expander feature of each I/O and a propagation delay increase of 2.0ns. OE, CLK, CLKEN, and MUX0 and MUX1 inputs can be driven directly from selected sets of I/O pins. Optional dedicated clock input pins give minimum clockto-output delays. CLK and CLKEN share the same set of I/O pins. CLKEN disables the register clock when CLKEN = 0.

After-Sales & Settlement Related

Payment

Payment

Payment Method

For alternative payment channels, please reach out to us at:

[email protected] Shipping & Packing

Shipping & Packing

Shipping Method

AVAQ determines and packages all devices based on electrostatic discharge (ESD) and moisture sensitivity level (MSL) protection requirements.

Warranty

Warranty

365-Day Product

Quality Guarantee

We promise to provide 365 days quality assurance service for all our products.

| Qty. | Unit Price | Ext. Price |

|---|---|---|

| 1+ | - | - |

The prices below are for reference only.

All bill of materials (BOM) can be sent via email to ![]() [email protected],

or fill below form to Quote for ispGDX160VA-5B208, guaranteed quotes back within

[email protected],

or fill below form to Quote for ispGDX160VA-5B208, guaranteed quotes back within

![]() 12hr.

12hr.

ISPGDX160VA-7B272

Lattice

Analog & Digital Crosspoint ICs PROGRAMMABLE GEN DIG CROSSPOINT

ISPGDX160VA-3B272

Lattice

Analog & Digital Crosspoint ICs PROGRAMMABLE GEN DIG CROSSPOINT

LX64C-5F100C

Lattice

Digital Crosspoint Single 64x64 11Gbps 100-Pin FBGA

LX128EV-5F208C

Lattice

Analog & Digital Crosspoint ICs 128 I/O SW Matrix 3.3V, 5ns, E-series

ispGDX160VA-5B272

Lattice Semiconductor Corp

Analog & Digital Crosspoint ICs PROGRAMMABLE GEN DIG CROSSPOINT