Payment Method

125 to 312.5-MHz FPGA-link deserializer with DDR LVDS parallel interface

Manufacturer:

Mfr.Part #:

DS32EL0124SQE/NOPB

Datasheet:

Protocols:

Catalog

Rating:

Catalog

Operating temperature range (°C):

-40 to 85

feature-function:

Deserializer

EDA/CAD Models:

Please fill in the short form below and we will provide you the quotation immediately.

The DS32EL0124/DS32ELX0124 integrates clock and data recovery modules for high-speed serial communication over FR-4 printed circuit board backplanes, balanced cables, and optical fiber. This easy-to-use chipset integrates advanced signal and clock conditioning functions, with an FPGA friendly interface.

The DS32EL0124/DS32ELX0124 deserializes up to 3.125 Gbps of high speed serial data to 5 LVDS outputs without the need for an external reference clock. With DC-balance decoding enabled, the application payload of 2.5 Gbps is deserialized to 4 LVDS outputs.

The DS32EL0124/DS32ELX01214 deserializers feature a remote sense capability to automatically signal link status conditions to its companion DS32EL0421/ELX0421 serializers without requiring an additional feedback path.

The parallel LVDS interface of these devices reduce FPGA I/O pins, board trace count and alleviates EMI issues, when compared to traditional single-ended wide bus interfaces.

The DS32EL0124/ELX0124 is programmable through a SMBus interface as well as through control pins.

All trademarks are the property of their respective owners.

| Protocols | Catalog | Rating | Catalog |

| Operating temperature range (°C) | -40 to 85 | feature-function | Deserializer |

| feature-number-of-drivers | 5 | feature-number-of-receivers | 2 |

| feature-number-of-elements-per-chip | 2 | feature-transmission-data-rate-mbps | 3125 |

| feature-maximum-propagation-delay-time-ns | feature-input-signal-type | CML|LVCMOS | |

| feature-differential-input-low-threshold-voltage-v | feature-differential-input-high-threshold-voltage-v | ||

| feature-maximum-differential-output-voltage-v | 0.31 | feature-maximum-input-current-ua | 40 |

| feature-supplier-temperature-grade | feature-packaging | Tape and Reel | |

| feature-rad-hard | feature-pin-count | 48 | |

| feature-cecc-qualified | No | feature-esd-protection | |

| feature-escc-qualified | feature-military | No | |

| feature-aec-qualified | No | feature-aec-qualified-number | |

| feature-auto-motive | No | feature-p-pap | No |

| feature-eccn-code | EAR99 | feature-svhc | Yes |

| feature-svhc-exceeds-threshold | No |

After-Sales & Settlement Related

Payment

Payment

Payment Method

For alternative payment channels, please reach out to us at:

[email protected] Shipping & Packing

Shipping & Packing

Shipping Method

AVAQ determines and packages all devices based on electrostatic discharge (ESD) and moisture sensitivity level (MSL) protection requirements.

Warranty

Warranty

365-Day Product

Quality Guarantee

We promise to provide 365 days quality assurance service for all our products.

| Qty. | Unit Price | Ext. Price |

|---|---|---|

| 1+ | - | - |

The prices below are for reference only.

All bill of materials (BOM) can be sent via email to ![]() [email protected],

or fill below form to Quote for DS32EL0124SQE/NOPB, guaranteed quotes back within

[email protected],

or fill below form to Quote for DS32EL0124SQE/NOPB, guaranteed quotes back within

![]() 12hr.

12hr.

SN65HVD230DR

TI

1000+ $0.403

ISO1050DUBR

Texas Instruments

1050+ $0.385

PCF8574AN

TI

8-bit 2.5- to 5.5-V I2C/SMBus I/O expander with interrupt

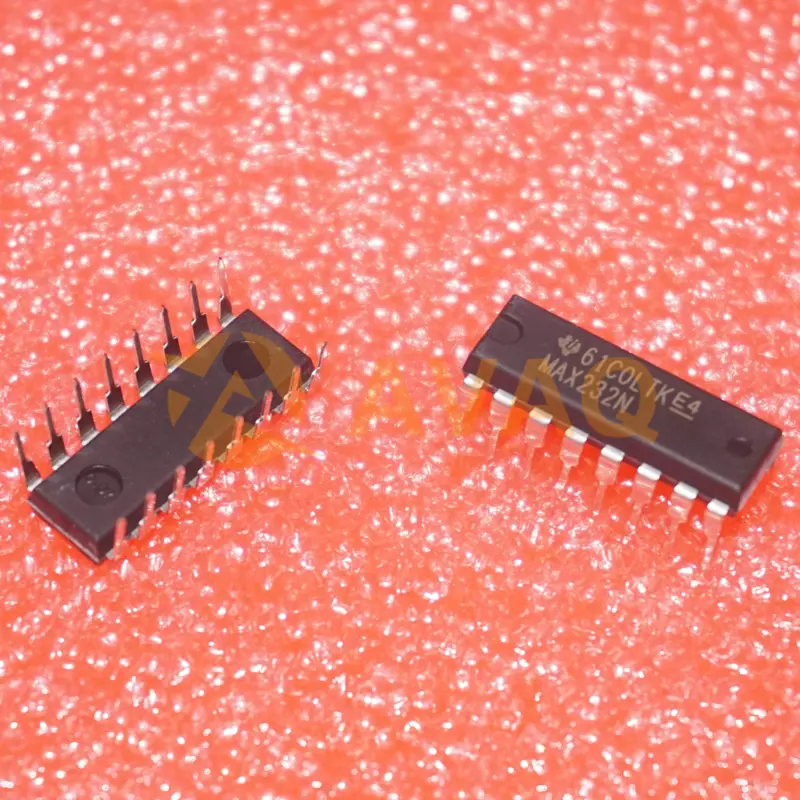

MAX232N

Texas Instruments

Dual Transmitter/Receiver RS-232 16-Pin PDIP Tube

TCA6424RGJR

Texas Instruments, Inc

24-bit translating 1.65- to 5.5-V I2C/SMBus I/O expander with interrupt, reset & config registers