Payment Method

Dual-Channel, 16-Bit, 1.0-GSPS, 1x-4x Interpolating Digital-to-Analog Converter (DAC)

Manufacturer:

Mfr.Part #:

DAC5682ZIRGCT

Datasheet:

Programmable:

Not Verified

Number of Bits:

16

Number of D/A Converters:

2

Settling Time:

10.4ns (Typ)

EDA/CAD Models:

Please fill in the short form below and we will provide you the quotation immediately.

The DAC5682Z is a dual-channel 16-bit 1.0 GSPS DAC with wideband LVDS data input, integrated 2x/4x interpolation filters, onboard clock multiplier, and internal voltage reference. The DAC5682Z offers superior linearity, noise, crosstalk, and PLL phase noise performance.

The DAC5682Z integrates a wideband LVDS port with on-chip termination. Full-rate input data can be transferred to a single DAC channel, or half-rate and 1/4-rate input data can be interpolated by onboard 2x or 4x FIR filters. Each interpolation FIR is configurable in either low-pass or high-pass mode, allowing selection of a higher order output spectral image. An on-chip delay lock loop (DLL) simplifies LVDS interfacing by providing skew control for the LVDS input data clock.

The DAC5682Z allows both complex or real output. An optional Fs/4 coarse mixer in complex mode provides coarse frequency upconversion and the dual DAC output produces a complex Hilbert Transform pair. An external RF quadrature modulator then performs the final single sideband up-conversion. The interpolation filters and complex coarse mixers efficiently provide frequency plan flexibility while enabling higher output DAC rates to simplify image rejection filtering.

The DAC5682Z is characterized for operation over the industrial temperature range of 40°C to 85°C and is available in a 64-pin QFN package. Other single-channel members of the family include the interpolating DAC5681Z and the noninterpolating DAC5681.

All other trademarks are the property of their respective owners

| Category | Integrated Circuits (ICs)Data AcquisitionDigital to Analog Converters (DAC) | Series | - |

| Programmable | Not Verified | Number of Bits | 16 |

| Number of D/A Converters | 2 | Settling Time | 10.4ns (Typ) |

| Output Type | Current - Unbuffered | Differential Output | Yes |

| Data Interface | LVDS - Parallel | Reference Type | External, Internal |

| Voltage - Supply, Analog | 3V ~ 3.6V | Voltage - Supply, Digital | 1.7V ~ 1.9V |

| INL/DNL (LSB) | ±4, ±2 | Architecture | Current Sink |

| Operating Temperature | -40°C ~ 85°C | Mounting Type | Surface Mount |

| Base Product Number | DAC5682 |

After-Sales & Settlement Related

Payment

Payment

Payment Method

For alternative payment channels, please reach out to us at:

[email protected] Shipping & Packing

Shipping & Packing

Shipping Method

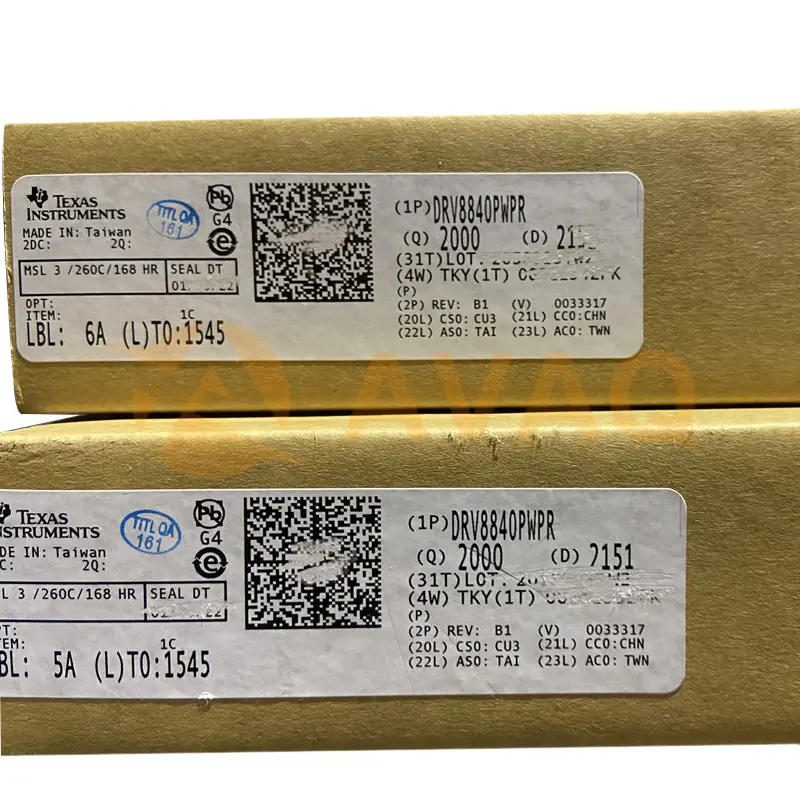

AVAQ determines and packages all devices based on electrostatic discharge (ESD) and moisture sensitivity level (MSL) protection requirements.

Warranty

Warranty

365-Day Product

Quality Guarantee

We promise to provide 365 days quality assurance service for all our products.

| Qty. | Unit Price | Ext. Price |

|---|---|---|

| 1+ | - | - |

The prices below are for reference only.

All bill of materials (BOM) can be sent via email to ![]() [email protected],

or fill below form to Quote for DAC5682ZIRGCT, guaranteed quotes back within

[email protected],

or fill below form to Quote for DAC5682ZIRGCT, guaranteed quotes back within

![]() 12hr.

12hr.

45 days delivery. Not test yet. I hope all be fine. Thanks.