Payment Method

Ethernet, SONET/SDH, Stratum IC 650MHz 3 Output 144-CABGA (13x13)

Manufacturer:

Mfr.Part #:

82P33831ABAG

Datasheet:

Programmable:

Not Verified

PLL:

Yes

Main Purpose:

Ethernet, SONET/SDH, Stratum

Input:

CMOS, LVDS, PECL

EDA/CAD Models:

Please fill in the short form below and we will provide you the quotation immediately.

The 82P33831 Synchronization Management Unit (SMU) provides tools to manage timing references, clock sources and timing paths for IEEE 1588 and Synchronous Ethernet (SyncE) based clocks. The device supports up to three independent timing paths that control: IEEE 1588 clock synthesis; SyncE clock generation; and general purpose frequency translation. The device supports physical layer timing with Digital PLLs (DPLLs) and it supports packet based timing with Digitally Controlled Oscillators (DCOs). Input-to-input, input-to-output and output-to-output phase skew can all be precisely managed. The device outputs low-jitter clocks that can directly synchronize 40GBASE-R, 10GBASE-R and 10GBASE-W and lower-rate Ethernet interfaces; as well as CPRI/OBSAI, SONET/SDH and PDH interfaces and IEEE 1588 Time Stamp Units (TSUs).

| Category | Integrated Circuits (ICs)Clock/TimingApplication Specific Clock/Timing | Series | - |

| Programmable | Not Verified | PLL | Yes |

| Main Purpose | Ethernet, SONET/SDH, Stratum | Input | CMOS, LVDS, PECL |

| Output | CMOS, LVDS, PECL | Number of Circuits | 3 |

| Ratio - Input:Output | 14:14 | Differential - Input:Output | Yes/Yes |

| Frequency - Max | 650MHz | Voltage - Supply | 1.8V, 3.3V |

| Operating Temperature | -40°C ~ 85°C | Mounting Type | Surface Mount |

| Base Product Number | 82P33831 |

After-Sales & Settlement Related

Payment

Payment

Payment Method

For alternative payment channels, please reach out to us at:

[email protected] Shipping & Packing

Shipping & Packing

Shipping Method

AVAQ determines and packages all devices based on electrostatic discharge (ESD) and moisture sensitivity level (MSL) protection requirements.

Warranty

Warranty

365-Day Product

Quality Guarantee

We promise to provide 365 days quality assurance service for all our products.

| Qty. | Unit Price | Ext. Price |

|---|---|---|

| 1+ | - | - |

The prices below are for reference only.

All bill of materials (BOM) can be sent via email to ![]() [email protected],

or fill below form to Quote for 82P33831ABAG, guaranteed quotes back within

[email protected],

or fill below form to Quote for 82P33831ABAG, guaranteed quotes back within

![]() 12hr.

12hr.

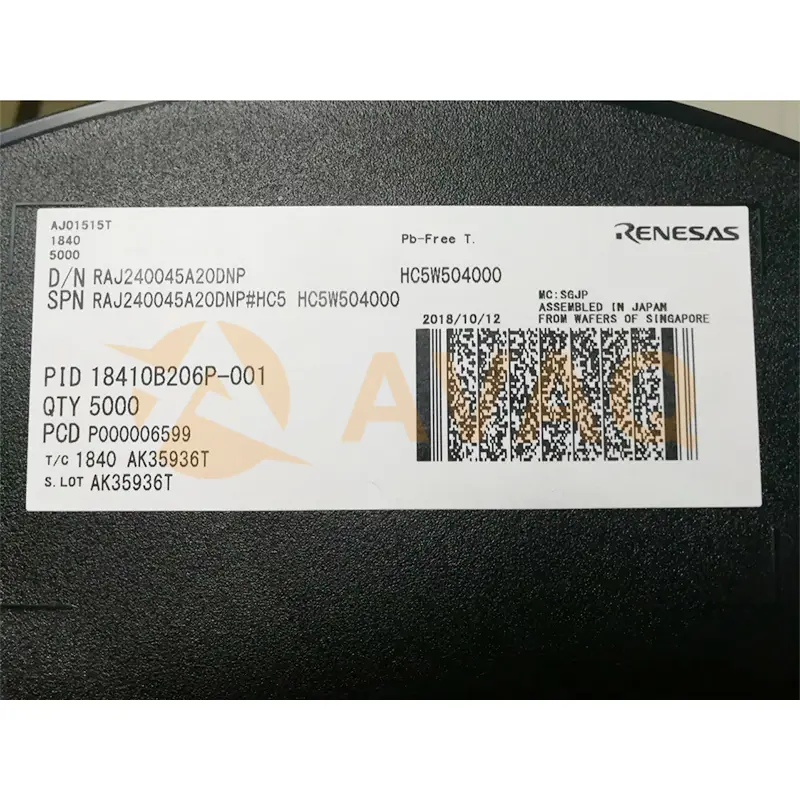

ICL8038CCPD

Renesas Electronics

1000+ $0.557

LM555N

Renesas Technology Corp

4000+ $0.080

9FGV0241AKLF

Renesas

Gen 1/2/3 PCIe Clock Generator with 2 Outputs

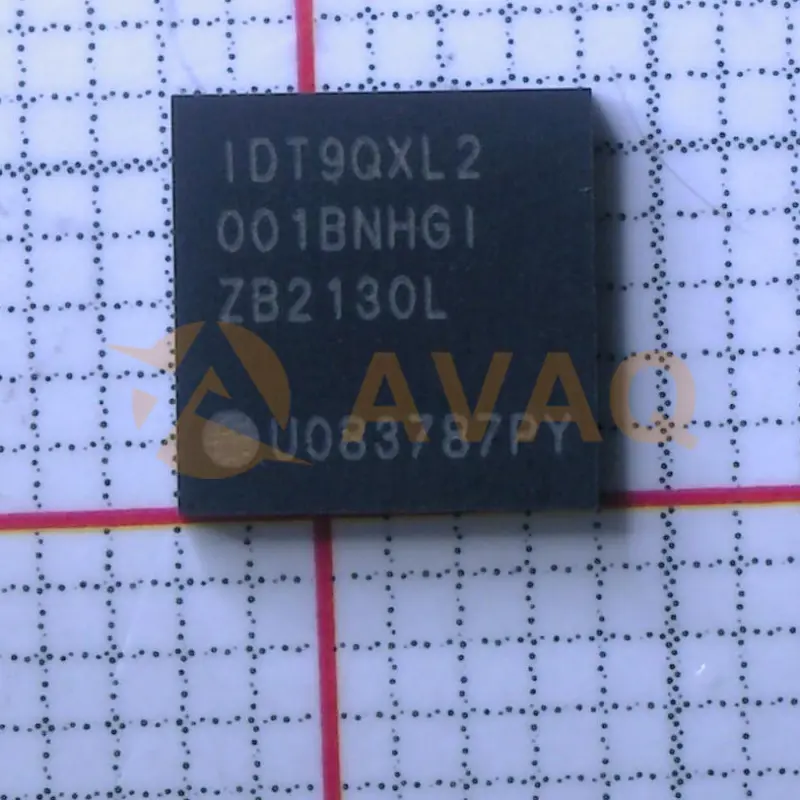

9QXL2001BNHGI8

RENESAS

Clock Fanout Buffer (Distribution) IC 1:20 400 MHz 80-VFQFN Dual Rows, Exposed Pad

ICM7555IPAZ

Renesas

8-Pin PDIP Package