Payment Method

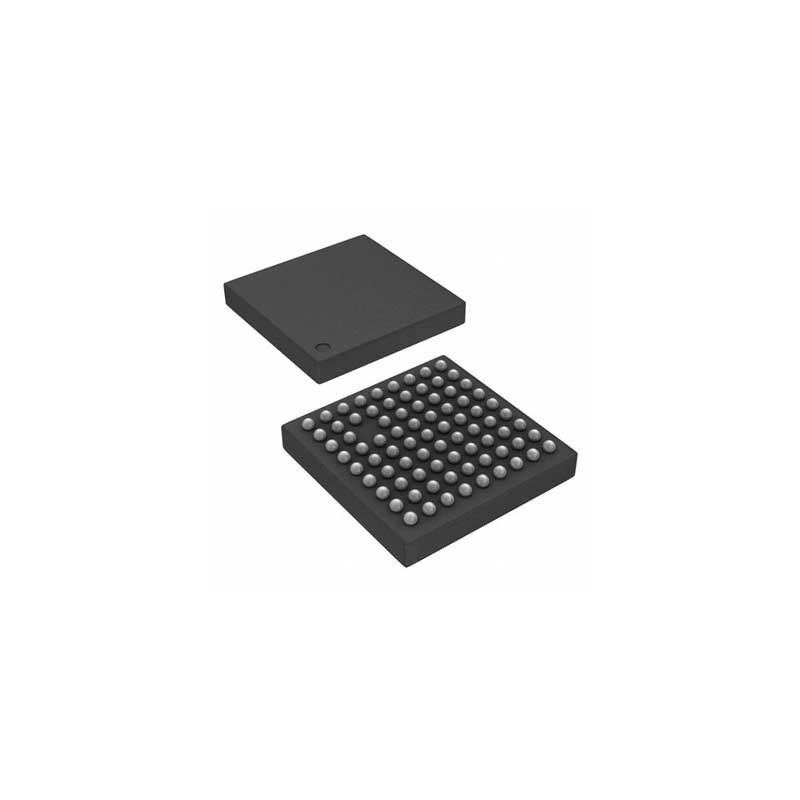

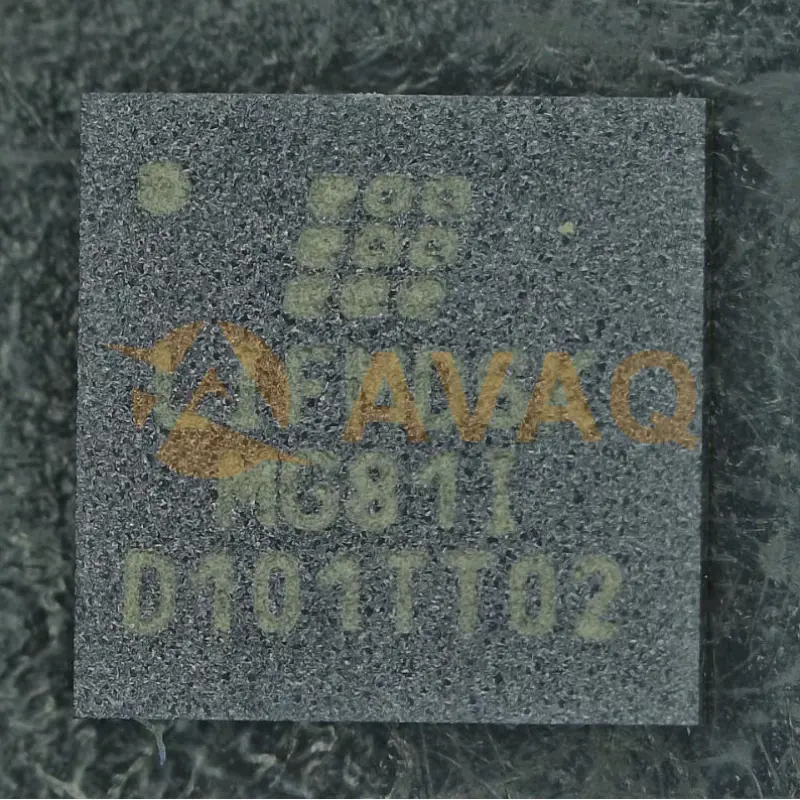

CPLD ispLSI® 1000 Family 6K Gates 128 Macro Cells 60MHz 5V 84-Pin CPGA

Manufacturer:

Mfr.Part #:

5962-9308501MXC

Datasheet:

Shipping Restrictions:

This product may require additional documentation to export from the United States.

Mounting Style:

SMD/SMT

Operating Supply Voltage:

5 V

Number of Macrocells:

128 Macrocell

EDA/CAD Models:

Please fill in the short form below and we will provide you the quotation immediately.

| Product Category | CPLD - Complex Programmable Logic Devices | Shipping Restrictions | This product may require additional documentation to export from the United States. |

| Mounting Style | SMD/SMT | Operating Supply Voltage | 5 V |

| Number of Macrocells | 128 Macrocell | Number of I/Os | 64 I/O |

| Supply Voltage - Max | 5.5 V | Supply Voltage - Min | 4.5 V |

| Minimum Operating Temperature | - 55 C | Maximum Operating Temperature | + 125 C |

| Maximum Operating Frequency | 60 MHz | Propagation Delay - Max | 20 ns |

| Height | 3.68 mm | Length | 29.97 mm |

| Number of Gates | 6000 | Number of Logic Array Blocks - LABs | 32 |

| Operating Supply Current | 220 mA | Product Type | CPLD - Complex Programmable Logic Devices |

| Factory Pack Quantity | 1 | Subcategory | Programmable Logic ICs |

| Width | 29.97 mm | Unit Weight | 0.488544 oz |

After-Sales & Settlement Related

Payment

Payment

Payment Method

For alternative payment channels, please reach out to us at:

[email protected] Shipping & Packing

Shipping & Packing

Shipping Method

AVAQ determines and packages all devices based on electrostatic discharge (ESD) and moisture sensitivity level (MSL) protection requirements.

Warranty

Warranty

365-Day Product

Quality Guarantee

We promise to provide 365 days quality assurance service for all our products.

| Qty. | Unit Price | Ext. Price |

|---|---|---|

| 1+ | - | - |

The prices below are for reference only.

All bill of materials (BOM) can be sent via email to ![]() [email protected],

or fill below form to Quote for 5962-9308501MXC, guaranteed quotes back within

[email protected],

or fill below form to Quote for 5962-9308501MXC, guaranteed quotes back within

![]() 12hr.

12hr.

LIF-MD6000-6JMG80I

Lattice Semiconductor Corp

891+ $4.638

LC4032V-75TN48C

Lattice

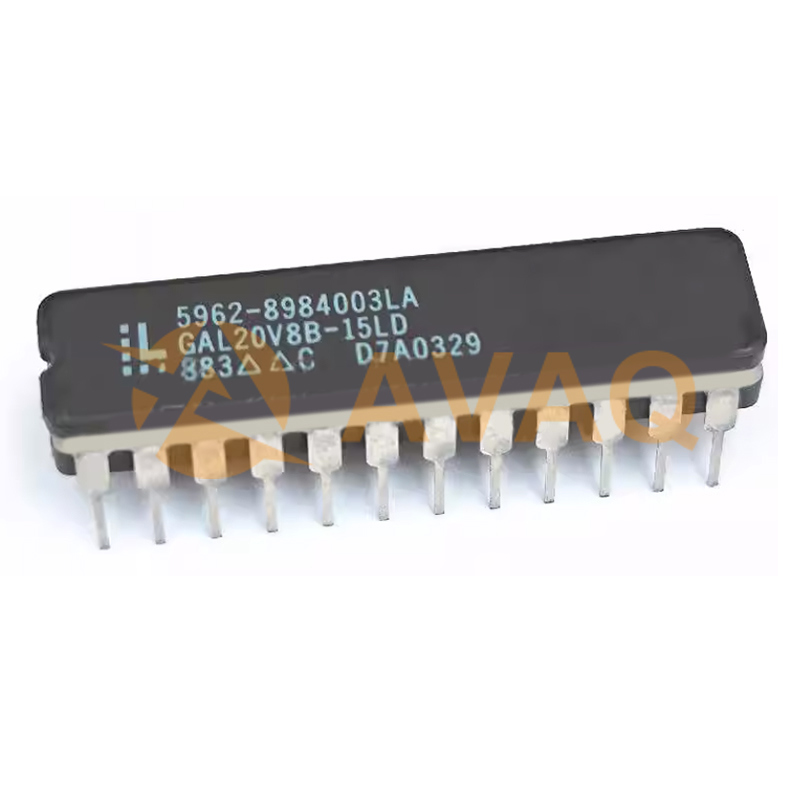

High Performance E2 CMOS PLD Generic Array Logic

GAL16V8D-25LPN

LATTICE SEMICONDUCTOR CORP

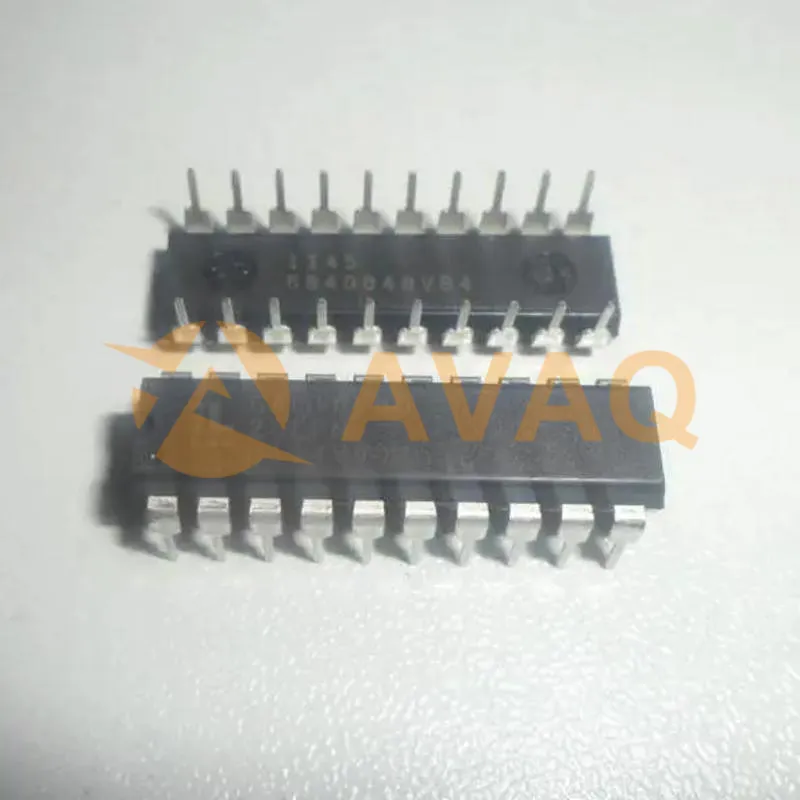

SPLD - Simple Programmable Logic Devices 16 Input 8 Output 5V Low Power 25ns

GAL16V8D-15LPN

Lattice

Concise summary: Programmable logic device, low power

LIF-MD6000-6MG81I

Lattice Semiconductor Corp

FPGA, CROSSLINK, 37 I/O, CSFBGA-81;