# **ON Semiconductor**

# Is Now

To learn more about onsemi™, please visit our website at www.onsemi.com

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/ or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application,

# Is Now Part of

# ON Semiconductor®

To learn more about ON Semiconductor, please visit our website at <a href="https://www.onsemi.com">www.onsemi.com</a>

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA Class 3 medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, emplo

**AN1025** April, 1996

# Maximum Power Enhancement Techniques for SuperSOT™-3 Power MOSFETs

Alan Li, Brij Mohan, Steve Sapp, Izak Bencuya, Linh Hong

# 1. Introduction

As packages become smaller, achieving efficient thermal performance for power applications requires that the designers employ new methods of meliorating the heat flow out of devices. Thus the purpose of this paper is to aid the user in maximizing the power handling capability of the SuperSOT $^{\text{TM}}$ -3 (SOT-23) Power MOSFET offered by Fairchild Semiconductor. This effort allows the user to take full advantage of the exceptional performance features of Fairchild's state-of-the-art Power MOSFET which offers very low on-resistance and improved junction-to-case ( $R_{\text{\tiny BJC}}$ ) thermal resistance. Ultimately the user may achieve improved component performance and higher circuit board packing density by using the thermal solution suggested below.

In natural cooling, the method of improving power performance should be focused on the optimum design of copper mounting pads. The design should take into consideration the size of the copper and its placement on either or both of the board surfaces. A copper mounting pad is important because the drain lead of the Power MOSFET is mounted directly onto the pad. The pad acts as a heatsink to reduce thermal resistance and leads to improved power performance.

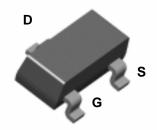

Figure 1. SuperSOT<sup>TM</sup>-3 Power MOSFET has the same package dimensions as the SOT-23 but the maximized copper lead frame reduces the junction-to-case thermal resistance  $R_{\theta,IC}$  to 75°C/W.

# 2. Theory

When a device operates in a system under the steady-state condition, the maximum power dissipation is determined by the maximum junction temperature rating, the ambient temperature, and the junction-to-ambient thermal resistance.

$$P_{Dmax} = (T_{Jmax} - T_{A}) / R_{\theta JC} (2.1)$$

The term junction refers to the point of thermal reference of the semiconductor. Equation 2.1 can also be applied to the transient-state:

$$P_{Dmax}(t) = [T_{Imax} - T_{\Delta}] / R_{AIC}(t) (2.2)$$

where  $P_{\text{Dmax}}(t)$  and  $R_{\text{eJC}}(t)$  are time dependent. By using the transient thermal resistance curves shown in the data sheet, a transient temperature change can be calculated. The transient thermal behavior is a complicated subject because  $R_{\text{eJA}}(t)$  increases non-linearly with time and the conditions of the power pulse. A more thorough treatment of transient power analysis is beyond the scope of this document and the reader can refer to [13] for details. Nevertheless, Fairchild provides a Discrete SPICE Thermal Model (LIT#570240-002) for general thermal evaluation. The user may find these models helpful in determining the dynamic power and temperature limits in the application.

$R_{_{\theta JA}} has two \ distinct \ elements, \ R_{_{\theta JC}} junction-to-case \ and \ R_{_{\theta CA}} case-to-ambient \ thermal \ resistance.$

$$R_{\theta JA} = R_{\theta JC} + R_{\theta CA} (2.3)$$

The case thermal reference of the SuperSOT™-3 Power MOSFET is defined as the point of contact between the drain lead of the package and the mounting surface.

$R_{e C A}$  is influenced by many variables such as ambient temperature, board layout, and cooling method. Due to the lack of an industry standard, the value of  $R_{e C A}$  is not easily defined and can affect  $R_{e J A}$  significantly. In addition, the case reference may be defined differently by various manufacturers. Under such conditions, it becomes difficult to define  $R_{e C A}$  from the component manufacturer standpoint. On the other hand,  $R_{e J C}$  is independent of users' conditions and can be accurately measured by the component manufacturer.

Therefore, in this paper an effort has been made to define a procedure which can be used to quantify the junction-to-ambient thermal resistance  $R_{_{\theta JA}}$  which is more useful to the circuit board designer.

# 3. Result

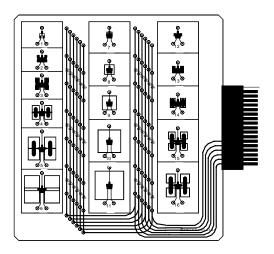

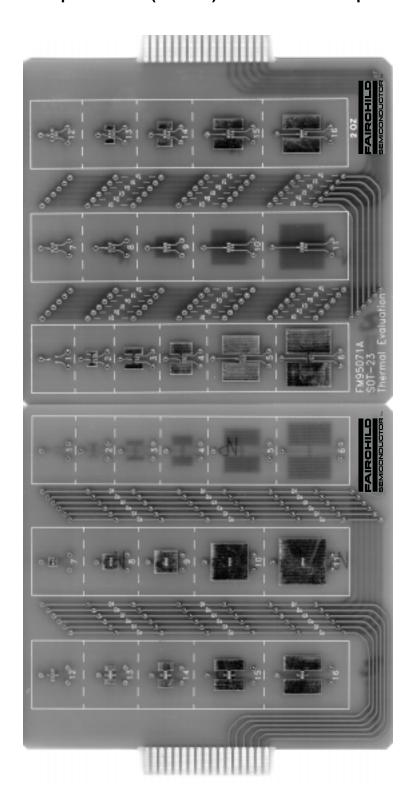

The scope of the investigation has been limited to the size of copper mounting pad and its relative surface placement on the board. In still air with no heatsink, the application of these heat dissipation methods is the most cost effective thermal solution. A total of sixteen different combinations of 2 Oz copper pad sizes and their placement were designed to study their influence on  $R_{\rm eJA}$  thermal resistance. The configurations of the board layout are shown in figure 2 and table 1. Layouts 1 to 6 have the copper pad sizes from 0.001 to 0.4 square inches on the top side of the board (top side is defined as the component side of the board). Layouts 7 to 11 have copper pad sizes from 0.02 to 0.4 square inches on the bottom side of the board. Layouts 12 to 16 have copper pad sizes from 0.02 to 0.4 square inches divided equally on both sides of the board.

Figure 2. Top Side of the 4.5"x5" SuperSOT<sup>TM</sup>-3 Thermal Board. Complete scale drawings are shown in section 5.

| Layout | 2 Oz Copper Mounting Pad<br>Area (in²) | Relative Placement on Board |

|--------|----------------------------------------|-----------------------------|

| 1-6    | 0.001, 0.02, 0.05, 0.1, 0.25, 0.4      | Тор                         |

| 7-11   | 0.02, 0.05, 0.1, 0.25, 0.4             | Bottom                      |

| 12-16  | 0.02, 0.05, 0.1, 0.25, 0.4             | 1/2 Top and 1/2 Bottom      |

Table 1: Thermal Board Configurations

$R_{\scriptscriptstyle \theta JA}$  was calculated from the relationship between power and the change of junction temperature. If readers are interested in the test conditions and method, they are encouraged to refer to appendix B for details.

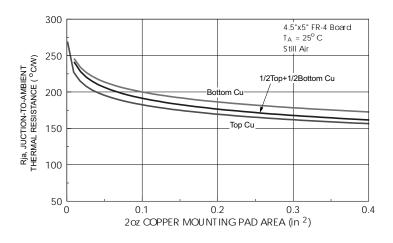

Figure 3. SuperSOT $^{\text{TM}}$ -3 Junction-to-Ambient thermal resistance versus copper mounting pad area and its surface placement.

Plots in figure 3 show the relationship of  $R_{\scriptscriptstyle \rm BJA}$  versus the copper mounting pad area and its surface placement on the board. It is apparent that increasing copper mounting pad area considerably lowers  $R_{\scriptscriptstyle \rm BJA}$  from approximately 270 to 160°C/W in the range from 0.001 to 0.4 square inches. In addition, placing all the copper on the top side of the board further reduces  $R_{\scriptscriptstyle \rm BJA}$  by 2 to 15°C/W when compared with the other two placements.

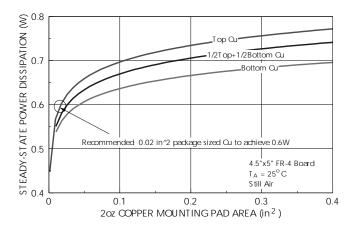

By substituting the thermal resistance, ambient temperature, and the maximum junction temperature rating into equation 2.1, the steady-state maximum power dissipation curves can be obtained and are shown in figure 4.

A 30% increase in the power handling can be achieved by increasing the copper pad area on top of the board from 0.001 to 0.02 in<sup>2</sup>, layout 2. This thermal pad fits directly under the package, so that no additional board space is required. For maximum performance, it is recommended to put extra copper on the bottom of the board connected to the top pad by through-hole thermal vias.

Figure 4. Maximum Power Dissipation Curves for SuperSOT™-3. 0.02 in² 2 Oz copper mounting pad area, layout 2, is recommended to achieve approximately 0.6W.

#### 4. Conclusion

Fairchild Semiconductor has attempted to define the thermal performance of the SuperSOT<sup>™</sup>-3 Power MOSFET, from a systems point of view. It has been demonstrated that significant thermal improvement can be achieved in the maximum power dissipation through the proper design of copper mounting pads on the circuit board. The results can be summarized as follows:

- Enlarged copper mounting pads, on either one or both sides of the board, are effective in reducing the case-to-ambient thermal resistance R<sub>eca</sub>

- Placement of the copper pads on the top side of the board gives the best thermal performance.

- The most cost effective approach of designing layout 2 0.02 square inches copper pad directly under the package, without occupying additional board space, can increase the maximum power from approximately 0.46 to 0.6W.

# 5. SuperSOT<sup>™</sup>-3 (SOT-23) Thermal Board Top and Bottom View

# Appendix A

# **Heat Flow Theory Applied to Power MOSFETs**

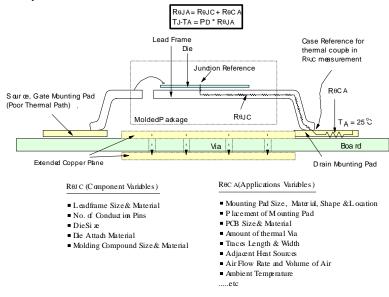

When a Power MOSFET operates with an appreciable current, its junction temperature is elevated. It is important to quantify its thermal limits in order to achieve acceptable performance and reliability. This limit is determined by summing the individual parts consisting of a series of temperature rises from the semiconductor junction to the operating environment. A one dimensional steady-state model of conduction heat transfer is demonstrated in figure 5. The heat generated at the device junction flows through the die to the die attach pad, through the lead frame to the surrounding case material, to the printed circuit board, and eventually to the ambient environment. There are also secondary heat paths. One is from the package to the ambient air. The other is from the drain lead frame to the detached source and gate leads then to the printed circuit board. These secondary heat paths are assumed to be negligible contributors to the heat flow in this analysis.

Figure 5: Cross-sectional view of a Power MOSFET mounted on a printed circuit board. Note that the case temperature is measured at the point where the drain lead(s) contact with the mounting pad surface.

The increase of junction temperature above the surrounding environment is directly proportional to dissipated power and the thermal resistance.

The steady-state junction-to-ambient thermal resistance,  $R_{_{\theta JA}}$ , is defined as  $R_{_{\theta JA}} = (T_{_J} - T_{_A}) / P$

where  $T_J$  is the average temperature of the device junction. The term junction refers to the point of thermal reference of the semiconductor device.  $T_A$  is the average temperature of the ambient environment. P is the power applied to the device which changes the junction temperature.

$R_{_{\theta,IA}}$  is a function of the junction-to-case  $R_{_{\theta,IC}}$  and case-to-ambient  $R_{_{\theta CA}}$  thermal resistance

$$\boldsymbol{R}_{\text{\theta JA}} = \boldsymbol{R}_{\text{\theta JC}} + \boldsymbol{R}_{\text{\theta CA}}$$

where the case of a Power MOSFET is defined at the point of contact between the drain lead(s) and the mounting pad surface.  $R_{_{\theta JC}}$  can be controlled and measured by the component manufacturer independent of the application and mounting method and is therefore the best means of comparing various suppliers component specifications for thermal performance. On the other hand, it is difficult to quantify  $R_{_{\theta CA}}$  due to heavy dependence on the application. Before using the data sheet thermal data, the user should always be aware of the test conditions and justify the compatibility in the application.

# Appendix B

#### **Thermal Measurement**

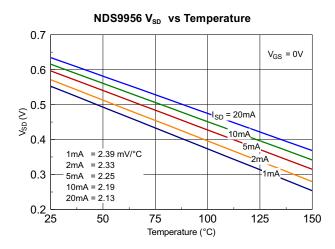

Prior to any thermal measurement, a K factor must be determined. It is a linear factor related to the change of intrinsic diode voltage with respect to the change of junction temperature. From the slope of the curve shown in figure 6, K factor can be determined. It is approximately 2.2mV/°C for most Power MOSFET devices.

Figure 6. K factors, slopes of a  $V_{SD}$  vs temperature curves, of a typical Power MOSFET

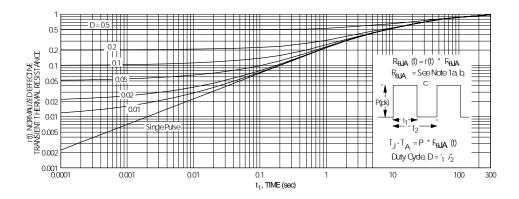

After the K factor calibration, the drain-source diode voltage of the device is measured prior to any heating. A pulse is then applied to the device and the drain-source diode voltage is measured 30us following the end of the power pulse. From the change of the drain-source diode voltage, the K factor, input power, and the reference temperature, the time dependent single pulsed junction-to-reference thermal resistance can be calculated. From the single pulse curve on figure 7, duty cycle curves can be determined. Note: a curve set in which  $R_{_{\theta JA}}$  is specified indicates that the part was characterized using the ambient as the thermal reference. The board layout specified in the data sheet notes will help determine the applicability of the curve set.

Figure 7. Normalized Transient Thermal Resistance Curves

# **B.1 Junction-to-Ambient Thermal Resistance Measurement**

Equipment and Setup:

- Tesec DV240 Thermal Tester

- 1 cubic foot still air environment

- Thermal Test Board with 16 layouts defined by the size of the copper mounting pad and their relative surface placement. For layouts with copper on the top and bottom planes, there are 0.02 inch copper plated vias (heat pipes) connecting the two planes. See figure 2 and table 1 on the thermal application note for board layout and description. The conductivity of the FR-4 PCB used is 0.29 W/m-C. The length is 5.00 inches ± 0.005; width 4.50 inches ± 0.005; and thickness 0.062 inches ± 0.005. 2Oz copper clad PCB.

The junction-to-ambient thermal measurement was conducted in accordance with the requirements of MIL-STD-883 and MIL-STD-750 with the exception of using 2 Oz copper and measuring diode current at 10mA.

A test device is soldered on the thermal test board with minimum soldering. The copper mounting pad reaches the remote connection points through fine traces. Jumpers are used to bridge to the edge card connector. The fine traces and jumpers do not contribute significant thermal dissipation but serve the purpose of electrical connections. Using the intrinsic diode voltage measurement described above, the junction-to-ambient thermal resistance can be calculated.

# **B.2 Junction-to-Case Thermal Resistance Measurement**

Equipment and Setup:

- Tesec DV240 Thermal Tester

- large aluminum heat sink

- type-K thermocouple with FLUKE 52 K/J Thermometer

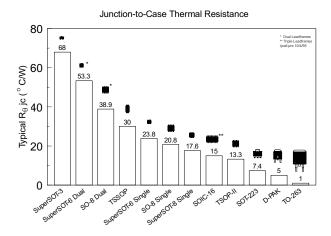

The drain lead(s) is soldered on a  $0.5 \times 1.5 \times 0.05$  copper plate. The plate is mechanically clamped to a heat sink which is large enough to be considered ideal. Thermal grease is applied in-between the two planes to provide good thermal contact. Theoretically the case temperature should be held constant regardless of the conditions. Thus a thermocouple is used and fixed at the point of contact between the drain lead(s) and the copper plate surface, to account for any heatsink temperature change. Using the intrinsic diode voltage measurement described earlier, the junction-to-case thermal resistance can be obtained. A plot of junction-to-case thermal resistance for

various packages is shown in figure 8. Note  $R_{_{\theta JC}}$  can vary with die size and the effect is more prominent as  $R_{_{\theta JC}}$  decreases.

Figure 8. Junction-to-case thermal resistance  $R_{_{\theta JC}}$  of various surface mount Power MOSFET packages.

#### References

- [1] K. Azar, S.S. Pan, J. Parry, H. Rosten, "Effect of Circuit Board Parameters on Thermal Performance of Electronic Components in Natural Convection Cooling," IEEE 10th annual Semi-Therm Conference, Feb. 1994.

- [2] A. Bar-Cohen, & A.D. Krauss, "Advances in Thermal Modeling of Electronic Components & Systems," Vol 1, Hemisphere Publishing, Washington, D.C., 1988.

- [3] R.T. Bilson, M.R. Hepher, J.P. McCarthy, "The Impact of Surface Mounted Chip Carrier Packaging on Thermal Management in Hybrid Microcircuit," Thermal Management Concepts in Microelectronics Packaging, InterFairchild Society for Hybrid Microelectronics, 1984.

- [4] R.A. Brewster, R.A. Sherif, "Thermal Analysis of A Substrate with Power Dissipation in the Vias," IEEE 8th Annual Semi-Therm Conf., Austin, Tx , Feb. 1992.

- [5] D. Edwards, "Thermal Enhancement of IC Packages, " IEEE 10th Annual Semi-Therm Conf., San Jose, Ca, Feb. 1994

- [6] S.S. Furkay, "Convective Heat Transfer in Electronic Equipment: An Overview," Thermal Management Concepts, 1984.

- [7] C. Harper, Electronic Packaging & Interconnection Handbook, McGraw-Hill, NY, 1991, Ch. 2.

- [8] Y.M. Kasem, R.K. Williams, "Thermal Design Principles and Characterization of Miniaturized Surface-Mount Packages for Power Electronics," IEEE 10th annual Semi-Therm Conf., San Jose, Ca, Feb. 1994.

- [9] V. Manno, N.R. Kurita, K. Azar, "Experimental Characterization of Board Conduction Effect," IEEE 9th Annual Semi-Therm Conf., 1993.

- [10] J.W. Sofia, "Analysis of Thermal Transient Data with Synthesized Dynamic Models for Semiconductor Devices," IEEE 10th Annual Semi-Therm Conf., San Jose, Ca, Feb. 1994.

- [11]G.R. Wagner, "Circuit Board Material/Construction and its Effect on Thermal Management," Thermal Management Concepts, 1984.

- [12] M. Wills, "Thermal Analysis of Air-Cooled Cbs," Electron Prod., pp. 11-18, May 1983.

- [13] Motorola Application Note AN-569.

#### **TRADEMARKS**

The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks.

ACEX<sup>TM</sup> ISOPLANAR<sup>TM</sup> CoolFET<sup>TM</sup> MICROWIRE<sup>TM</sup>

CROSSVOLT<sup>TM</sup> POP<sup>TM</sup>

E<sup>2</sup>CMOS<sup>™</sup> PowerTrench<sup>™</sup>

FACT<sup>TM</sup> QS<sup>TM</sup>

#### **DISCLAIMER**

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **PRODUCT STATUS DEFINITIONS**

#### **Definition of Terms**

| Datasheet Identification | Product Status            | Definition                                                                                                                                                                                                            |

|--------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information      | Formative or<br>In Design | This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                                    |

| Preliminary              | First Production          | This datasheet contains preliminary data, and supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design. |

| No Identification Needed | Full Production           | This datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design.                                                       |

| Obsolete                 | Not In Production         | This datasheet contains specifications on a product that has been discontinued by Fairchild semiconductor. The datasheet is printed for reference information only.                                                   |

ON Semiconductor and in are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdt/Patent-Marking.pdf">www.onsemi.com/site/pdt/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and exp

# **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative